勞務(wù)分包商入庫資料 建筑物清潔服務(wù)規(guī)范與要求

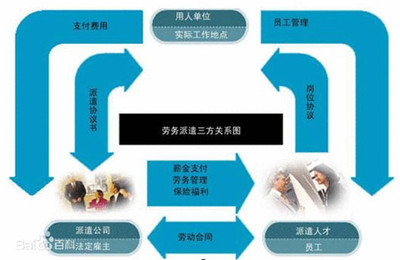

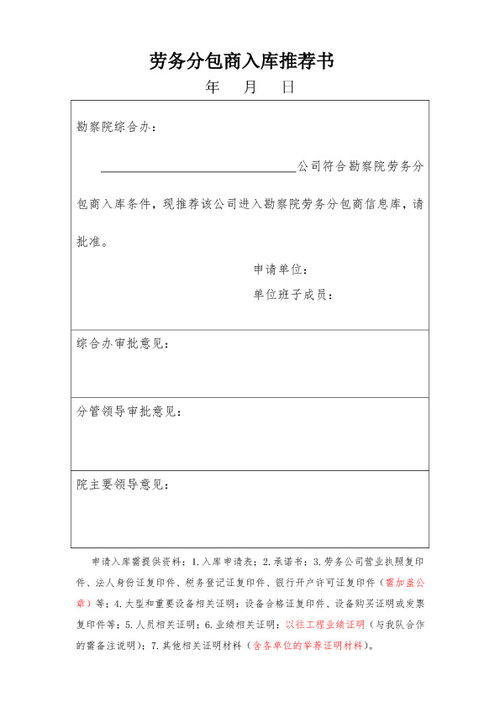

為規(guī)范勞務(wù)分包管理,確保建筑物清潔服務(wù)質(zhì)量,擬入庫的勞務(wù)分包商需提交以下資料,經(jīng)審核合格后方可納入合格供應(yīng)商名錄。本要求適用于提供建筑物內(nèi)外清潔、保養(yǎng)及相關(guān)服務(wù)的勞務(wù)分包單位。

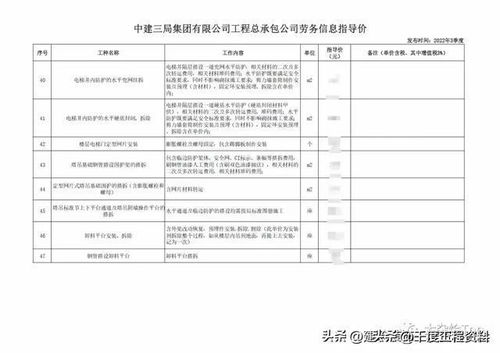

一、基本資質(zhì)文件

- 合法有效的《企業(yè)法人營業(yè)執(zhí)照》副本復(fù)印件,經(jīng)營范圍需包含建筑物清潔服務(wù)或相關(guān)項(xiàng)目。

- 法定代表人身份證明復(fù)印件及授權(quán)委托書(如由代理人辦理)。

- 企業(yè)資質(zhì)證書:如具備《清潔清洗行業(yè)資質(zhì)等級(jí)證書》等相關(guān)行業(yè)認(rèn)證,需提供復(fù)印件。

- 安全生產(chǎn)許可證或相關(guān)安全管理體系認(rèn)證文件(如適用)。

二、專業(yè)能力證明

- 人員配置:提供清潔服務(wù)團(tuán)隊(duì)的組織架構(gòu)圖、關(guān)鍵崗位人員名單及其資格證書復(fù)印件(如高空作業(yè)證、特種設(shè)備操作證等)。

- 技術(shù)實(shí)力:簡述主要服務(wù)內(nèi)容(如玻璃幕墻清洗、石材養(yǎng)護(hù)、高空外墻清洗、室內(nèi)日常保潔等),并提供過往類似項(xiàng)目的技術(shù)方案或作業(yè)指導(dǎo)書樣本。

- 設(shè)備清單:列明自有或租賃的主要清潔設(shè)備、工具及安全防護(hù)裝備清單(如高壓清洗機(jī)、吸塵器、升降平臺(tái)、安全繩等),并注明其狀態(tài)及檢測(cè)情況。

三、業(yè)績與信譽(yù)材料

- 近三年內(nèi)完成的建筑物清潔服務(wù)項(xiàng)目業(yè)績表,需包含項(xiàng)目名稱、地點(diǎn)、合同金額、服務(wù)內(nèi)容及業(yè)主方聯(lián)系方式。

- 至少兩份由過往客戶出具的履約評(píng)價(jià)證明或推薦信。

- 銀行出具的資信證明或近一年的企業(yè)納稅證明復(fù)印件。

- 無重大安全事故及違法違規(guī)記錄的承諾書或相關(guān)證明。

四、管理體系文件

- 質(zhì)量保證體系:提供清潔服務(wù)質(zhì)量控制流程、檢查標(biāo)準(zhǔn)及應(yīng)急預(yù)案。

- 安全管理體系:包括員工安全培訓(xùn)記錄、高空作業(yè)安全規(guī)程、危險(xiǎn)源識(shí)別與控制措施等文件。

- 環(huán)境管理措施:符合環(huán)保要求的清潔劑使用說明及廢棄物處理方案。

五、合作與承諾

- 提交針對(duì)本次入庫的服務(wù)承諾書,明確響應(yīng)時(shí)間、服務(wù)標(biāo)準(zhǔn)及保修條款。

- 提供應(yīng)急服務(wù)預(yù)案,確保突發(fā)情況下的快速處理能力。

- 同意遵守發(fā)包方相關(guān)管理制度并簽訂分包合同的意向聲明。

所有提交資料需加蓋企業(yè)公章,并按順序裝訂成冊(cè)。發(fā)包方將對(duì)資料真實(shí)性進(jìn)行核實(shí),并可能安排現(xiàn)場(chǎng)考察或面試。通過審核的分包商將納入供應(yīng)商庫,具備參與后續(xù)項(xiàng)目投標(biāo)或直接委托的資格。

建筑物清潔服務(wù)不僅關(guān)乎環(huán)境衛(wèi)生,更直接影響建筑壽命與使用者體驗(yàn)。選擇專業(yè)、可靠的勞務(wù)分包商,是保障工程品質(zhì)與運(yùn)營安全的重要基石。請(qǐng)各申請(qǐng)單位認(rèn)真準(zhǔn)備,確保資料完整規(guī)范,共同促進(jìn)行業(yè)健康發(fā)展。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://m.genshen.com.cn/product/37.html

更新時(shí)間:2026-04-08 21:09:33